Key Takeaways

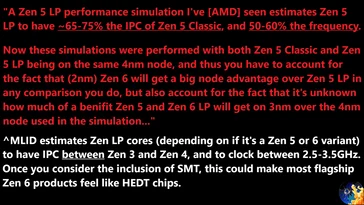

1. Zen 6, named Medusa Point, will debut on laptops with an increased core count, featuring Zen 6, Zen 6c, and LP cores.

2. Four new CPUs (Ryzen 9 475, Ryzen 9 465, Ryzen 7 450, Ryzen 5 445) have been identified as 28 Watt components for laptop use.

3. These CPUs are likely part of the Gorgon Point series, using the FP8 socket, and are essentially refreshed Strix Point dies.

4. The Gorgon Point lineup includes three tiers: Gorgon Point 1, Gorgon Point 2 (trimmed version), and Gorgon Point 3 (refresh of Krackan Point).

5. Medusa Point will be released under the Ryzen AI 500 name, with a GPU limited to RDNA 3.5, as RDNA 4 is not expected for laptops soon.

Multiple leaks have revealed that Zen 6 is set to debut on laptops under the name Medusa Point. The most recent leak mentioned an increase in core count and highlighted the addition of three distinct CPU cores (Zen 6, Zen 6c, and LP) on the chip. Additionally, another leak has provided insights into AMD’s upcoming laptop SKUs that won’t feature Zen 6 cores.

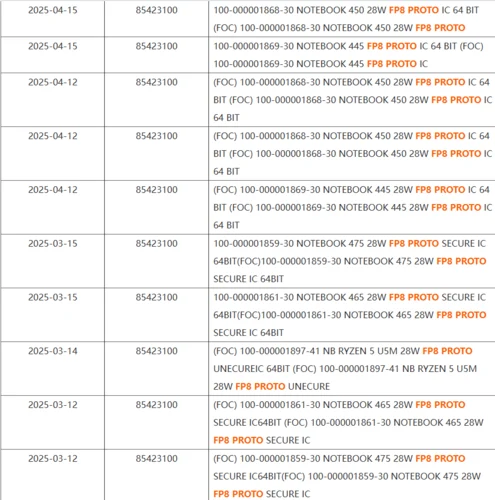

New CPUs Spotted

Renowned leaker Olrak29_ has identified four interesting CPUs: the Ryzen 9 475, Ryzen 9 465, Ryzen 7 450, and Ryzen 5 445 (these names are provisional) on a shipping list. While the specific core counts remain unclear, all of them are designed as 28 Watt components, confirming that they are intended for laptop usage.

Gorgon Point Details

Another source, @9550pro, added that these CPUs are probably part of the Gorgon Point series since they utilize the FP8 socket, which is the same as that used by Strix Point. This leaker also mentioned that these processors are basically refreshed Strix Point dies, suggesting they will launch with a combination of Zen 5 and Zen 5c cores.

Lineup Breakdown

Earlier, @Olrak29_ shared information about three tiers within the Gorgon Point lineup: Gorgon Point 1, Gorgon Point 2, and Gorgon Point 3. It is suggested that Gorgon Point 2 will be a trimmed-down version of Gorgon Point 1, whereas Gorgon Point 3 will serve as a refresh of the Krackan Point.

If this information is accurate, it indicates that Medusa Point will be released under the Ryzen AI 500 name, aligning with AMD’s typical naming conventions. The GPU will be limited to RDNA 3.5, as RDNA 4 is not expected to make its way to laptops in the near future.

Source:

Link