According to some previous rumors, Samsung has achieved success with its 3nm process nodes and the development of its 2nm process nodes is also progressing smoothly.

However, a recent report from Businesskorea indicates that Samsung Foundry’s 3nm process remains significantly inferior to TSMC’s, both in yield rate and power efficiency. For those unfamiliar, higher yield rates mean more functional chips per wafer, lowering the cost per chip and increasing profitability.

Industry Preferences

As a result, it is expected that most fabless manufacturers including NVIDIA, AMD, Intel, Qualcomm, MediaTek, and Apple will continue to rely on TSMC for their 3nm chips. It has also been reported that Google will switch to TSMC for its 2025 flagship chipset Tensor G5. Notably, the Tensor G4, which will power the upcoming Pixel 9 series, will still be manufactured by Samsung Foundry and will be based on an updated 4nm process.

Production Challenges

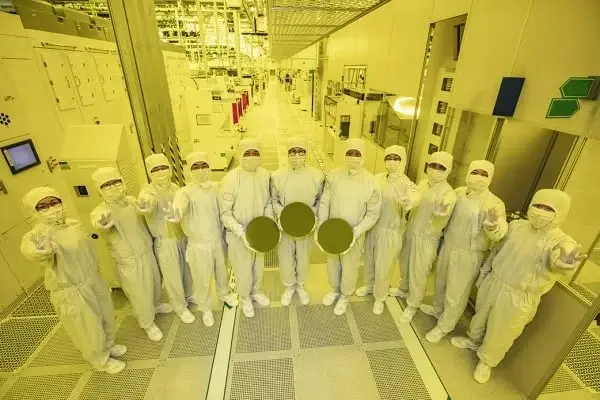

Samsung talked about the mass production of their 3nm chips 3 years ago. Back in June 2022, Samsung Foundry was the first in the industry to apply the 3nm gate-all-around (GAA) process to mass production. However, due to the limitations, the company is still struggling to secure customers for the end product. The first generation 3nm process node (SF3E) has performed below the company’s expectations when it comes to performance and power efficiency. It has reportedly been adopted by some niche scenarios like chips for cryptocurrency mining. However, a widespread adoption will still require more improvements in power efficiency and yield rates.

Yield Rate Issues

The relatively lower yield rates and power efficiency of Samsung Foundry’s process nodes have long been problematic and are considered the main reasons for the performance gap between Snapdragon (those that are fabricated by TSMC) and Exynos-powered Galaxy devices.

According to a previous report, Qualcomm is considering a dual-sourcing strategy by partnering with Samsung Foundry alongside TSMC. While this is aimed at securing the company’s business by not relying on a single manufacturer, the company’s CEO mentioned “the current focus must be on the foundry production at TSMC.”